Quartus

下载

一、官网下载(可下载Windows,linux版本. 需注册):

点击

二、网盘下载

9.1版本下载地址:

链接:https://pan.baidu.com/s/1CE_TPvpIwLXiwXtNMdSJ-A

提取码:cpj9

13.0版本下载地址:

链接:https://pan.baidu.com/s/1f-0-3VclXivQFzFX83BeCg

提取码:d1yd

13.1版本下载地址:

链接:https://pan.baidu.com/s/1V4hcfuNhY0EQ7oGmnjlpVQ

提取码:k39z

18.1lite版本下载地址:

链接:https://pan.baidu.com/s/1JMH75Y7l1cW8x_uveJ1pVg

提取码:i83y

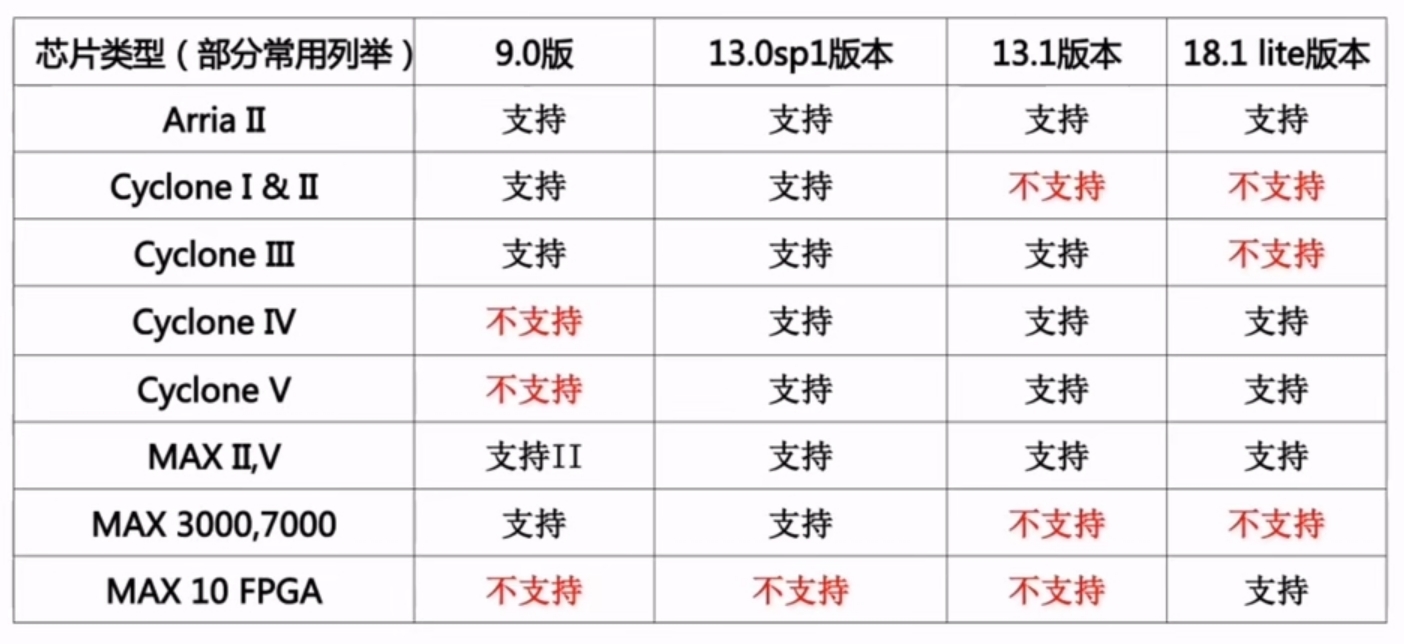

版本推荐:

注意安装路径仅限字母数字下划线,不能出现中文等特殊字符,连空格都不行

EDA

什么是EDA?

EDA(Electronic Design Automation)技术作为现代电子设计技术的核心,依赖功能强大的计算机软件。它是一门综合性学科。利用EDA技术进行电子系统设计的最后目标,是完成专用集成电路ASIC或者印刷电路板PCB的设计和实现。

硬件描述语言Verilog:

硬件描述语言HDL是EDA技术的重要组成部分,目前常用的主要有

VHDL、HDL等。2001年,Verilog成为基层电路建模与设计中最流行的硬件描述语言。

Verilog部分语法参照C语言语法设立(但与C有本质区别)。在语言易读性、层次化和结构化设计方面表现了强大的生命力和应用潜力,大大简化硬件设计任务,且具有良好的适应性。

常见HDL:

- 另一重要的硬件描述语言是VHDL(超高速集成电路硬件描述语言)。

- VHDL具有与具体硬件电路无关和设计平台无关的特性,并且具有良好的电路行为能力和系统描述能力。

- Verilog与VHDL各有优缺点。

- 综合(Synthesis):把抽象的实体结合成单个统一的实体。将用行为和功能层次表达的电子系统转换为低层次的便于具体实现的模块组合装配的过程。【类比编写大型程序】

- 综合器:能自动将一种设计表述形式向另一种转换的软件,或者协助进行手工转换的软件。

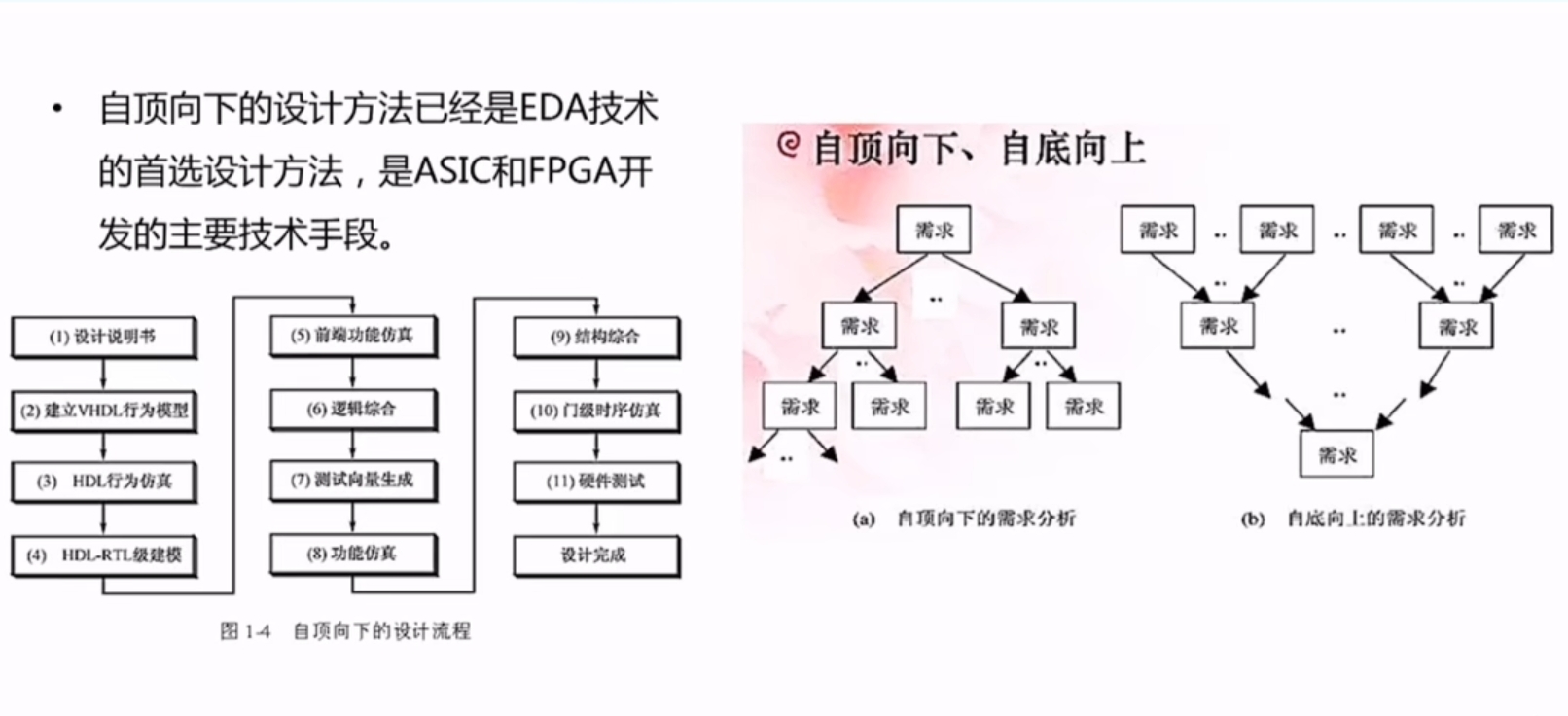

自顶向下设计技术

EDA优点

1.保证设计过程的正确性,大大降低设计成本,缩短设计周期。

2.有各类库的支持。

3.极大地简化设计文档的管理。

4.日益强大的逻辑设计仿真测试技术。

5.设计者拥有完全的自主权,再无受制于人之虞。

6.良好的可移植与可测试性,为系统开发提供了可靠的保证。

7.能将所有设计环节纳入统一的自顶向下的设计方案中。

8.EDA不但在整个设计流程上充分利用计算机的自动设计能力,而且在各个设计层次上利用计算机完成不同内容的仿真模拟,在系统板设计结束后仍可利用计算机对硬件系统进行完整的测试。

- 手工设计有缺陷,EDA技术则不同。

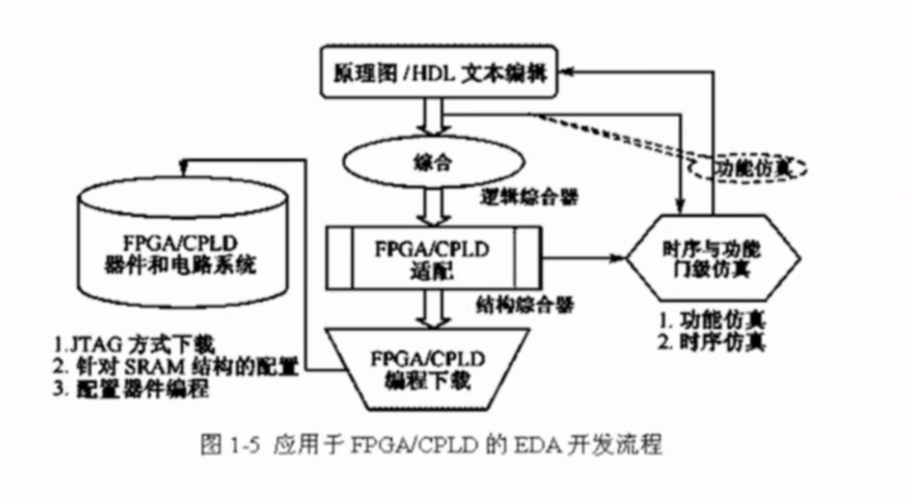

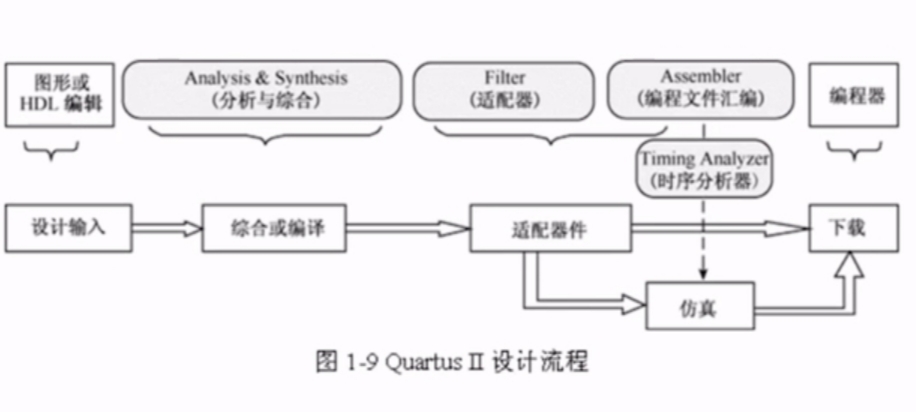

- 设计输入、综合、适配、仿真、编程下载、硬件测试

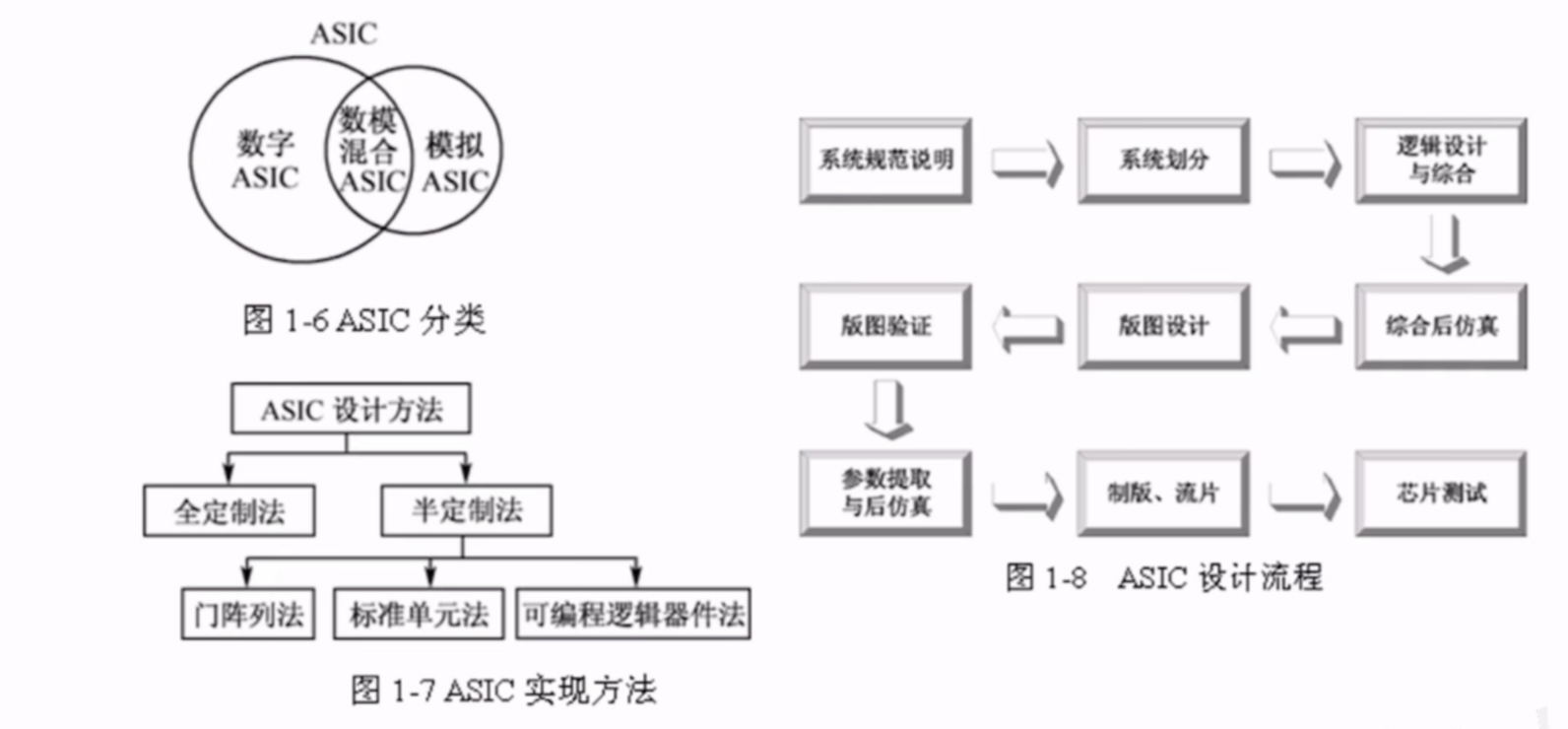

ASIC及其设计流程:

常见EDA工具:

- 设计输入编辑器

- HDL综合器:Quartus2

- 仿真器:modelsim

- 适配器(布局布线器):Altium Designer

- 下载器:Quartus2

- 其他

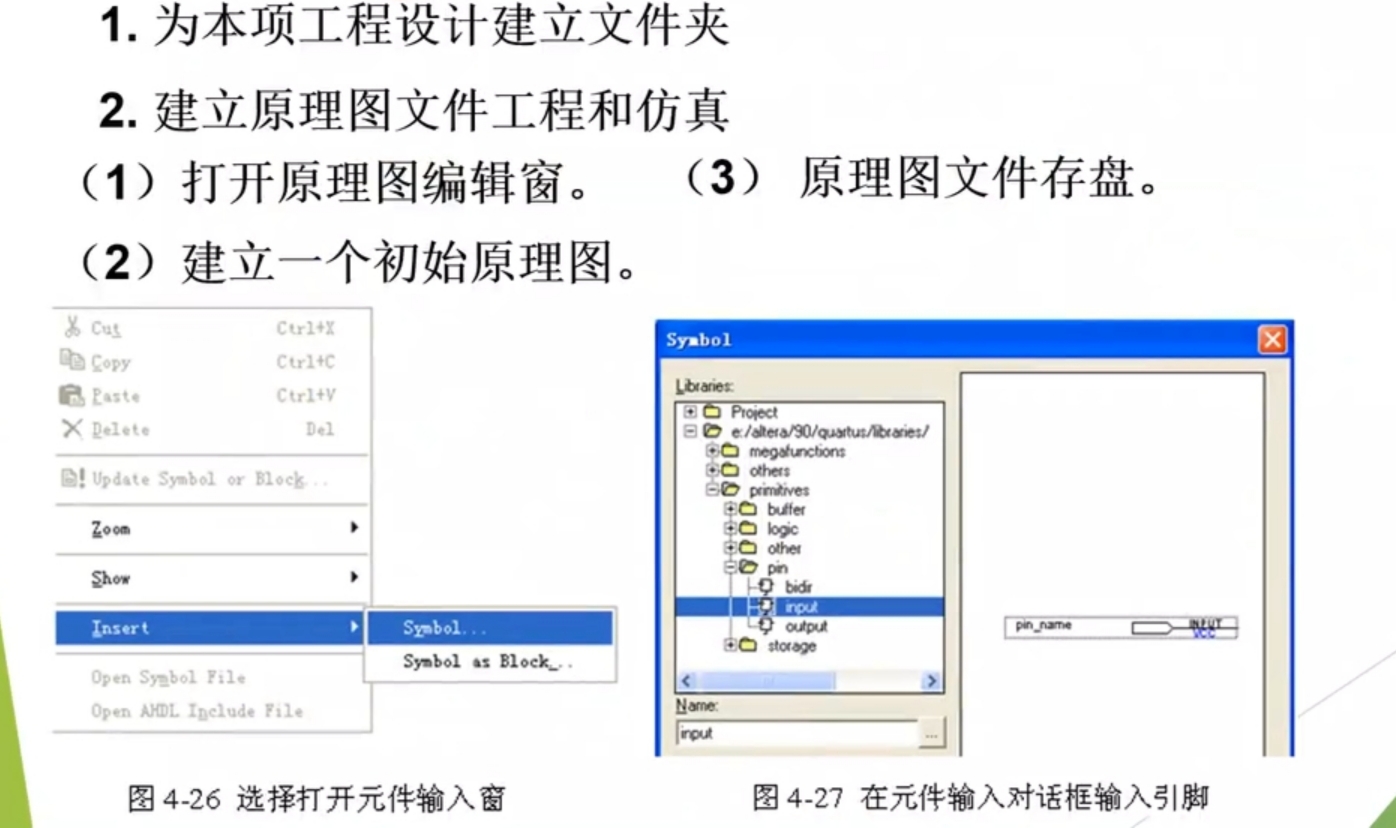

1.新建:

点击:File->New,选择Block Diagram/Schematic File,点击OK

2.点击连接库()或者左键空白处:

找到libraries->primitives->logic,选择需要的芯片;libraries->primitives->pin,输入输出端.(megafunctions:包括一些参数可设置的功能模块.others:maxplus2(Quartus软件前身:74系列芯片).primitives:logic:xnor:同或门;xor:异或门;pin:引脚(bibdr:双向引脚);storage:触发器:dff:D触发器)

如果发现有虚的芯片在动,说明点击了重复模式,点击Esc取消即可

3.连线:鼠标左键点住拖动就行

4.双击输入/输出端口,可重新命名端口名,将输入端口命名为 clk,输出端口命名为 q[3…0]。此时

输出端口为总线模式,可同时观察 4 个输出。特别注意:QA、QB、QC、QD 4 个输出端需要命名为

q[0]、q[1]、 q[2]、 q[3],与总线输出 q[3…0]对应。

5.点击左上角保存:出现:Do you want to create a new project with this file?点击Yes,点击Next,

根据要求设置就行,然后点击Next,最后Finish。

6.然后点击紫色三角进行编译(默认编译顶层设计实体,如果要编译其他设计文件需要将其置顶:点击Files下的文件,右键选择Set as Top_Level Entity)

7.点击File->New->University Program VWF,然后点击Edt->Insert->Insert Node or Bus(或者将鼠标放到左边Name下面的空白处,双击左键),点击Node Finder,点击List,全部移入(>>),点击OK

8.设置:选中,然后点击:

设置相关属性:

点击功能仿真(只仿真功能)(它的右边为时序仿真:会考虑芯片的时延):

建议:采用时序仿真

点击Yes,最后保存,等待仿真结束.

放大:Ctrl+鼠标滚轮

移位:选中+拖拽

Verilog语言编程基础

1.模块语句及其表达式

1 | module 模块名 (模块端口名表); |

2.端口语句、端口信号名和端口模式

1 | input 端口名1,端口名2,...; |

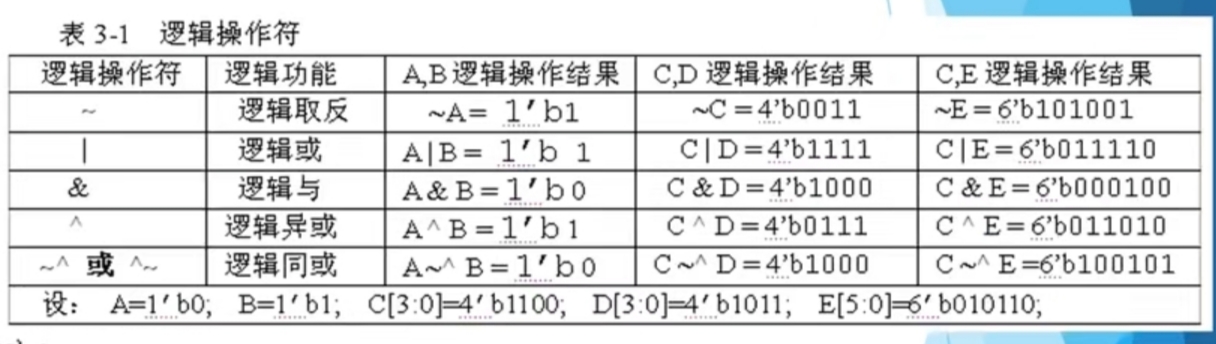

3.逻辑操作符

4.连续赋值语句

1 | assign 目标变量名 = 驱动表达式; |

5.关键字

6.标识符

7.注释符号

8.规范的程序书写格式

9.文件取名和存盘

eg:半加器电路的Verilog描述

1 | module h_adder (A,B,SO,CO); |

多路选择器:

1.reg型变量定义

1 | reg 变量名1,变量名2,...; |

2.过程语句

1 | always@ (敏感信号及敏感信号列表或表达式) |

3.块语句begin_end

1 | begin [:块名] |

4.case条件语句

1 | case (表达式) |

5.Verilog的四种逻辑状态:0,1,z,x

6.并位操作运算符

{a1,b1,4{a2,b2}}={a1,b1,{a2,b2},{a2,b2},{a2,b2},{a2,b2}}={a1,b1,a2,b2,a2,b2,a2,b2,a2,b2}

7.Verilog的数字表达式

1 | <位宽>'<进制><数字> |

eg:4选1多路选择器

1 | //case: |

1.新建:File->New->Verilog HDL File->OK

2.保存:File->Save,文件名需与模块名一致,其他按之前保存步骤

设置要更改为:

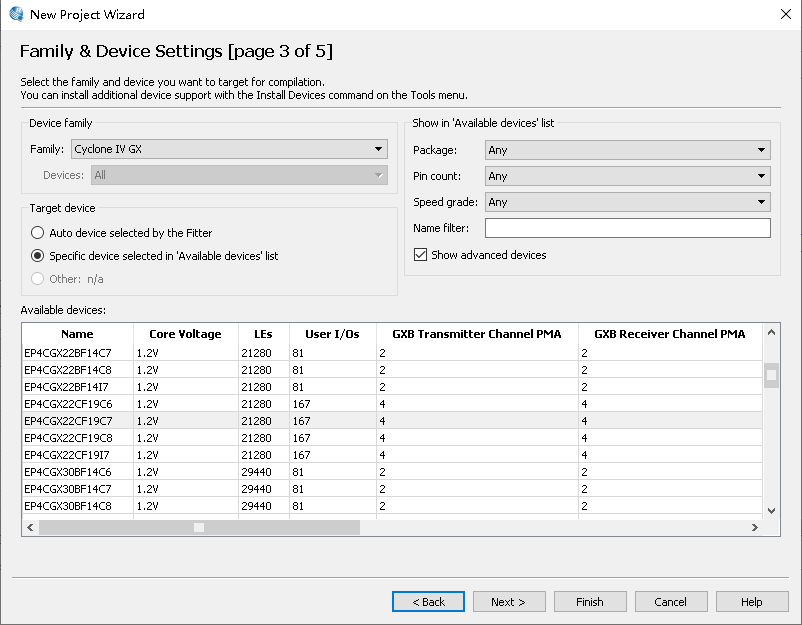

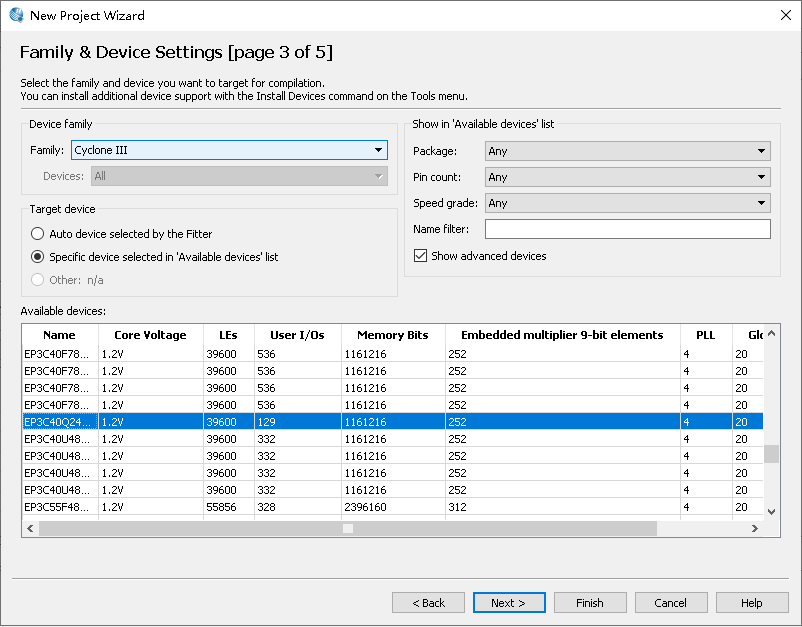

选择Cyclone 3 -> EP3C40Q240C8,最后点击紫色三角进行编译

3.点击File->New->University Program VWF,然后点击Edt->Insert->Insert Node or Bus,点击Node Finder,点击3个点(…),选中MUX41a,按下OK,然后点击List,然后点击 >> ,点击OK就行了

4.然后设置终止时间:Edt->Set End Time (10us)

5.点击:

设置相关属性:

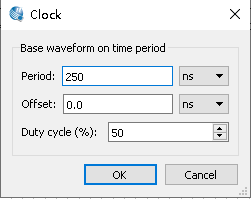

a: period:90ns;Duty Cycle:50%(b:200ns,70%;c:400ns,20%;d:780ns,85%;s0:4us,50%;s1:2us,50%),点击OK;

6.然后点击仿真,出现叫你保存的页面:点击Yes保存即可

1.按位逻辑操作符

2.等式操作符

等于()不等于(!=)全等(=)不全等(!==)

3.wire定义网线型变量

1 | wire 变量名1,变量名2,...; |

条件语句

1.if条件语句

1 | if(s) Y=A; else Y=B; |

2.过程赋值语句

(1)阻塞式赋值(=)用于assign语句

(2)非阻塞式赋值(<=)块语句

3.数据类型表示方式

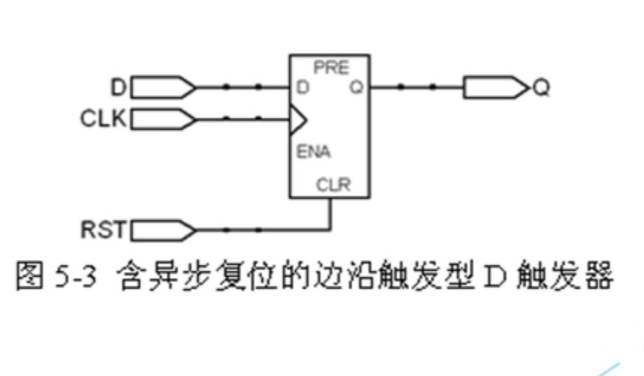

时序电路的Verilog表达

eg:D触发器

1 | module DFF1(CLK,D,Q); |

用UDP表述D触发器

1 | primitive EDGE_UDP(Q,D, CLK,RST) ; |

1 | module DFF_UDP (Q,D,CLK, RST) ; |

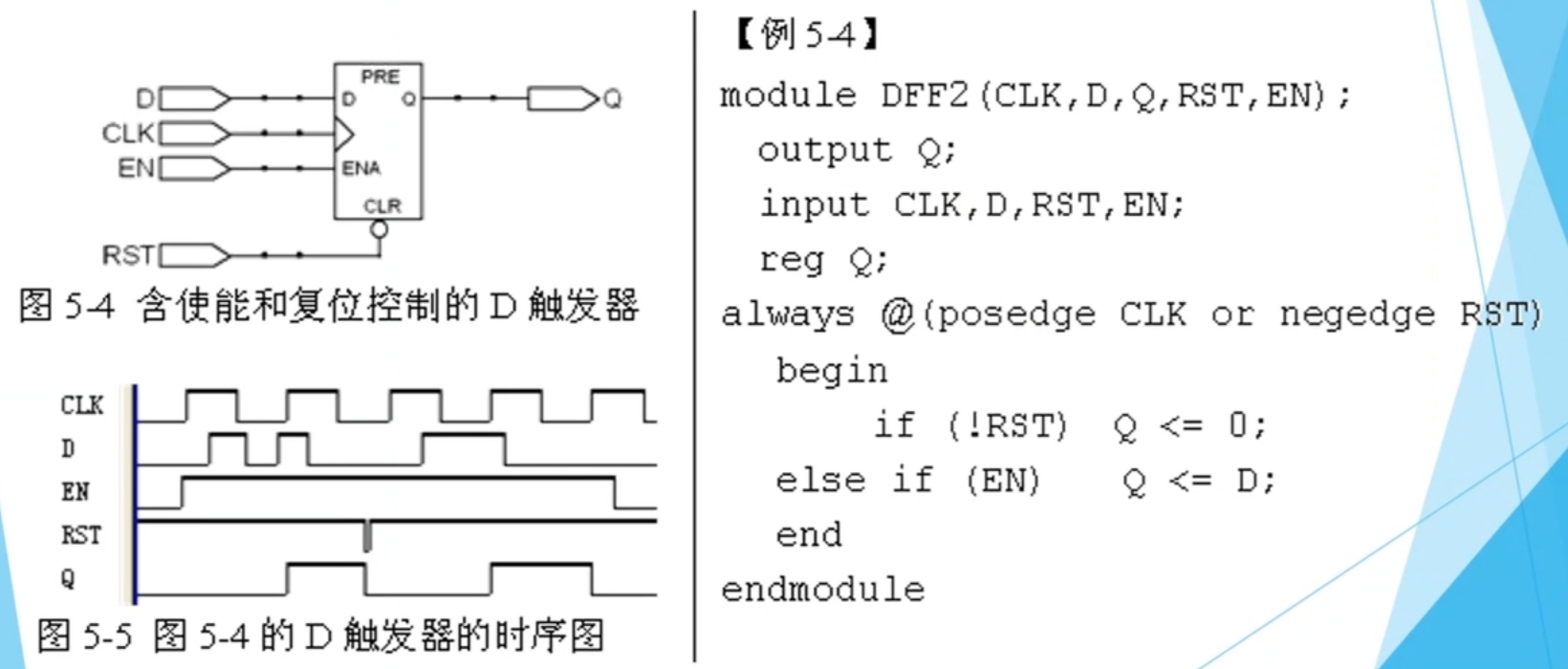

含异步复位和时钟使能的D触发器及其Verilog表述

RST:异步复位端;EN:时钟使能端

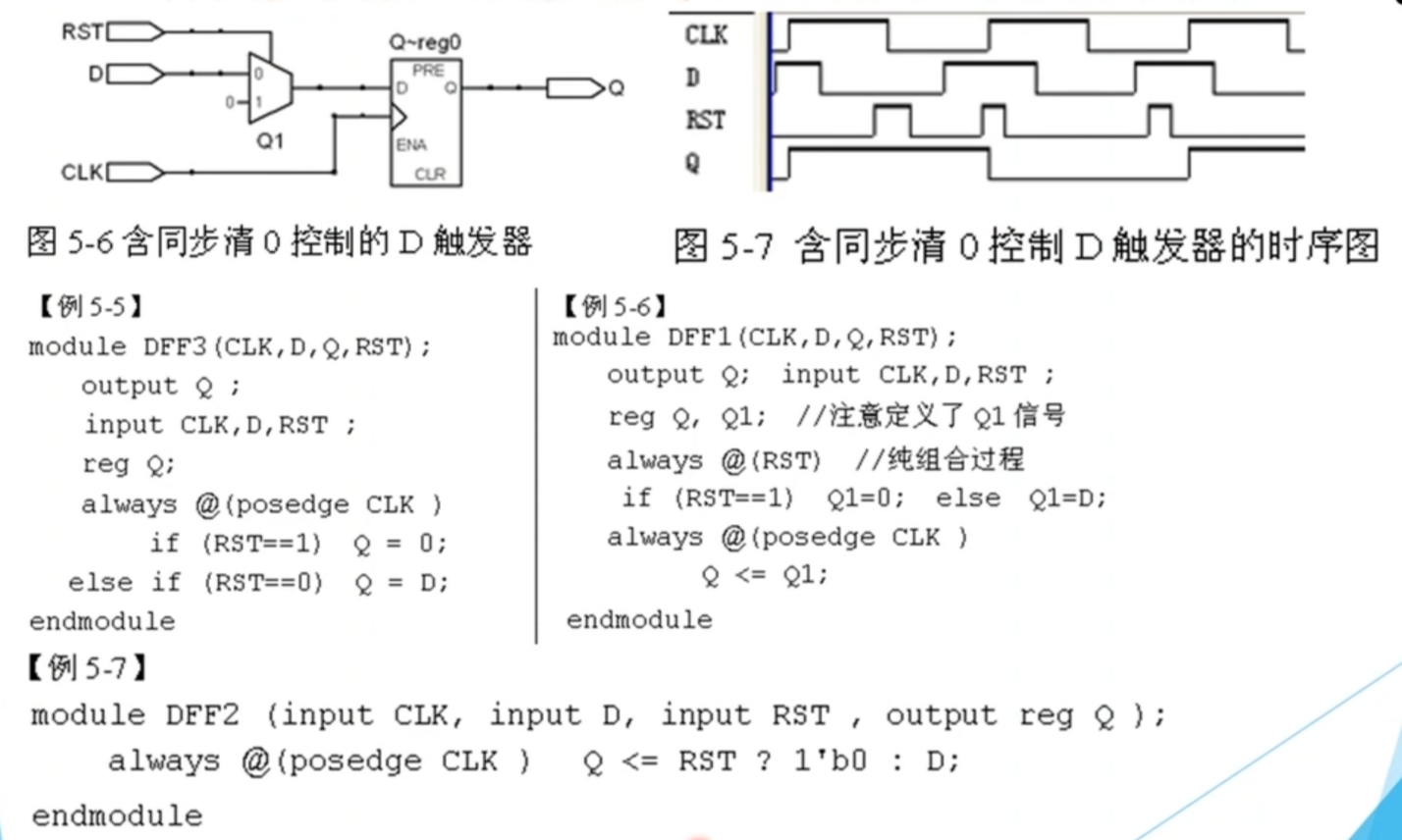

含同步复位(同步清零)控制的D触发器及其Verilog表述

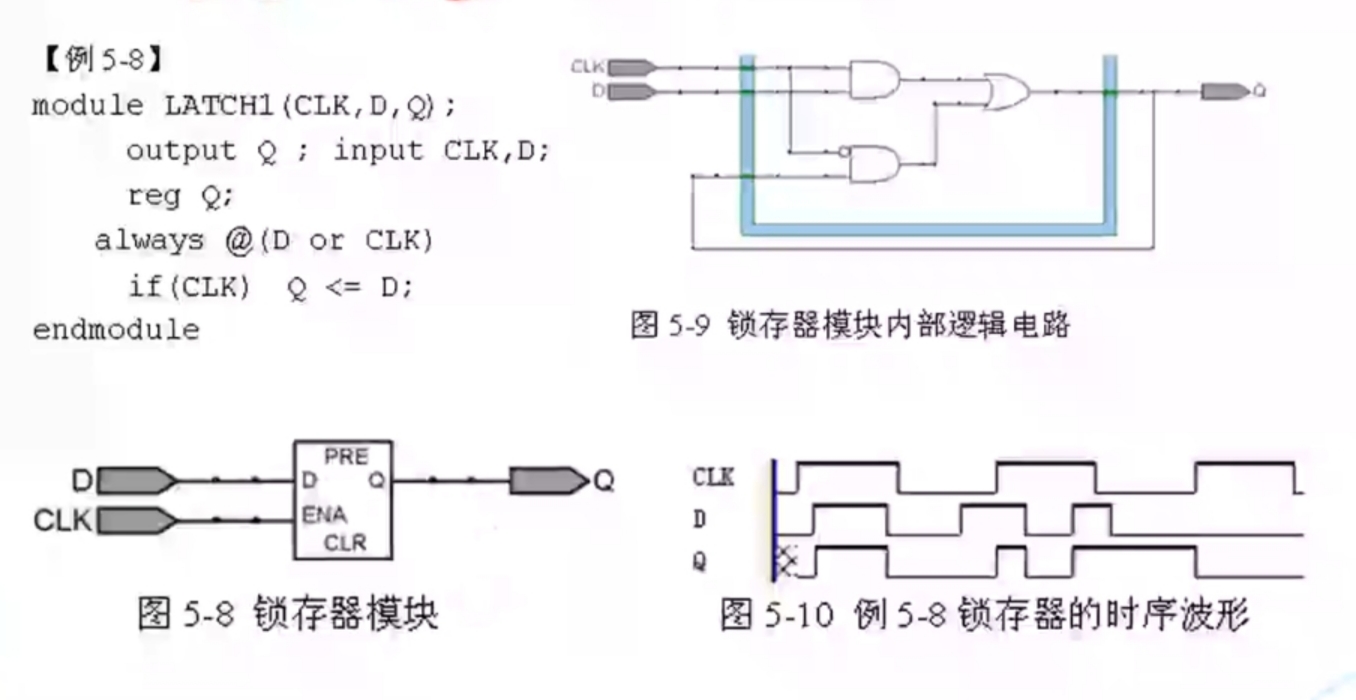

基本锁存器及其Verilog描述

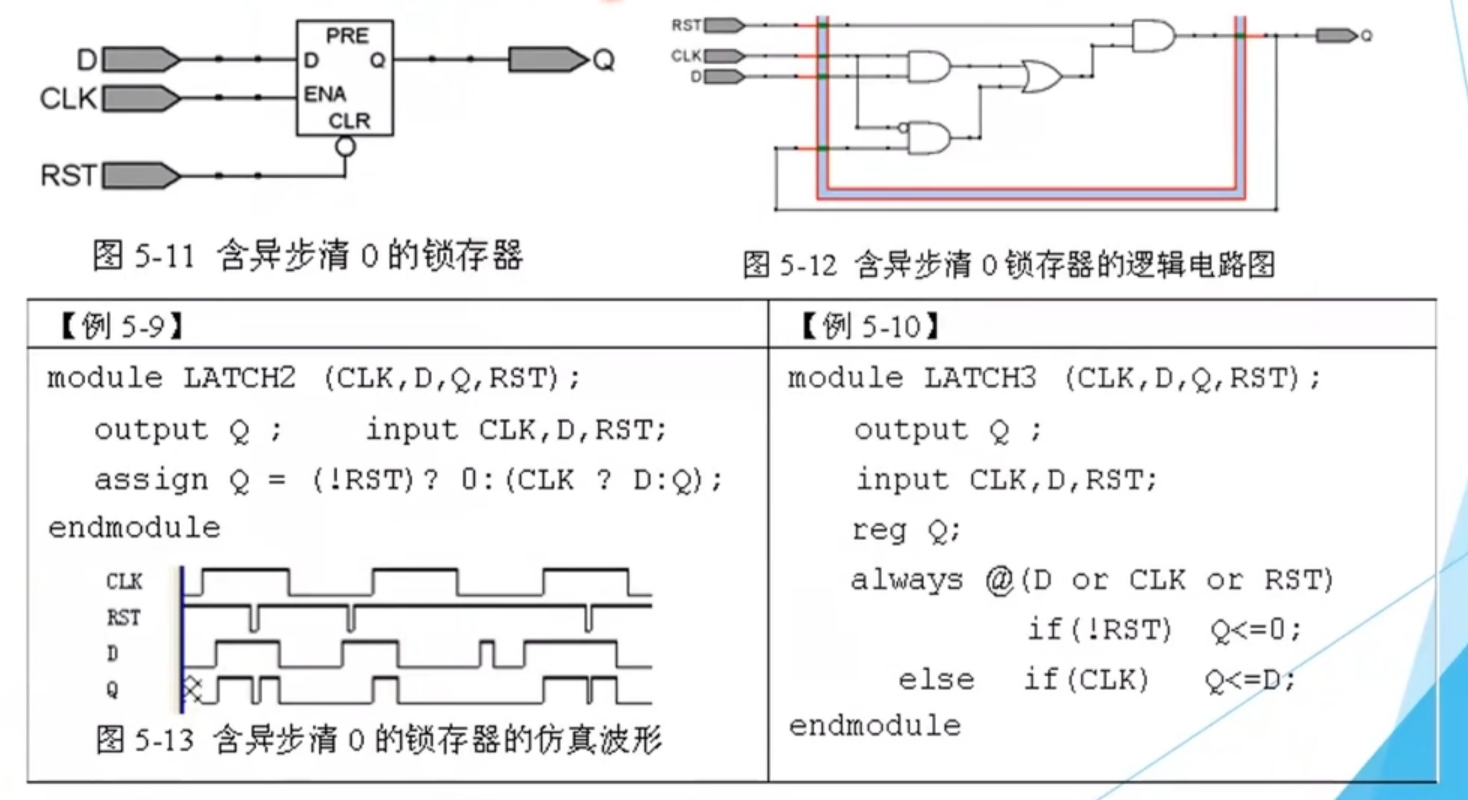

含清0控制的锁存器及其Verilog表述

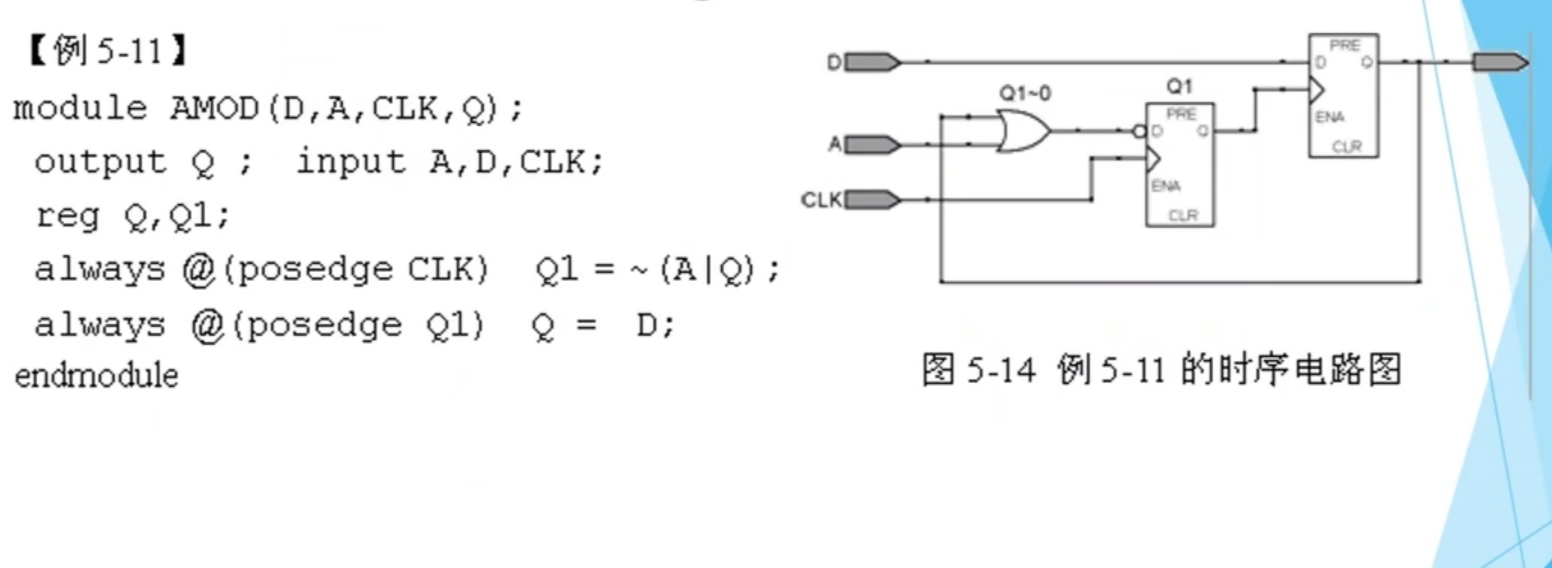

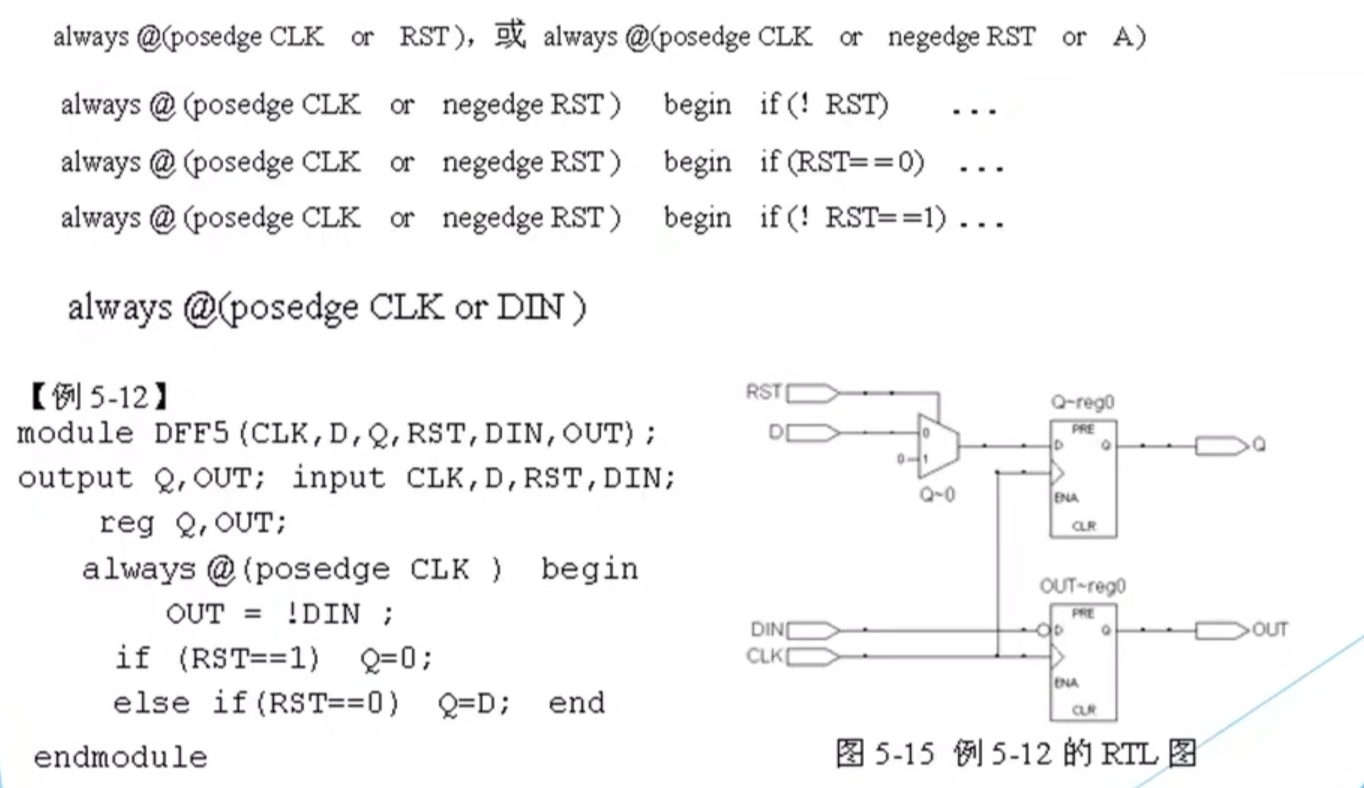

异步时序电路的Verilog表述特点

时钟过程表述的特点和规律

always @ (posedge CLK or DIN):不允许在敏感信号表中定义除了异步时序控制信号以外的信号

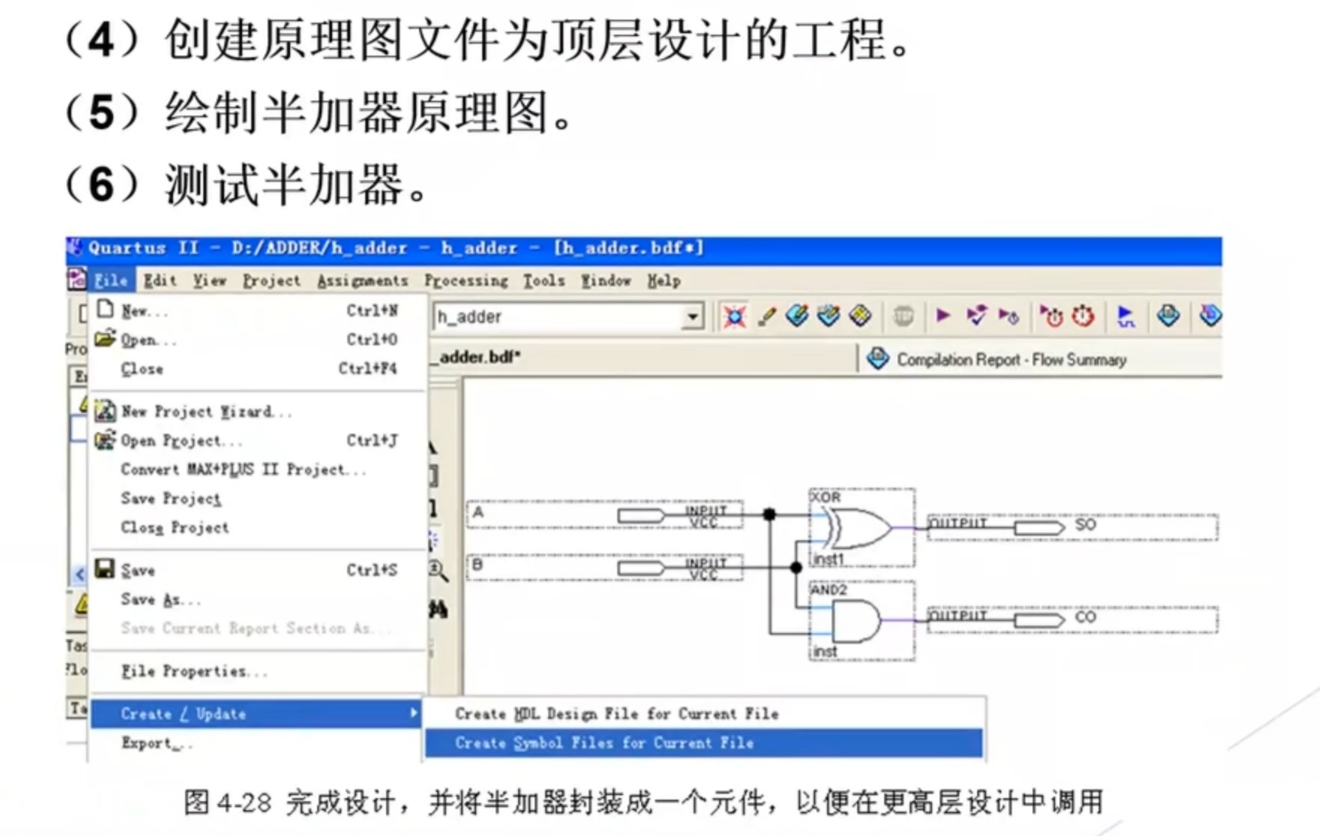

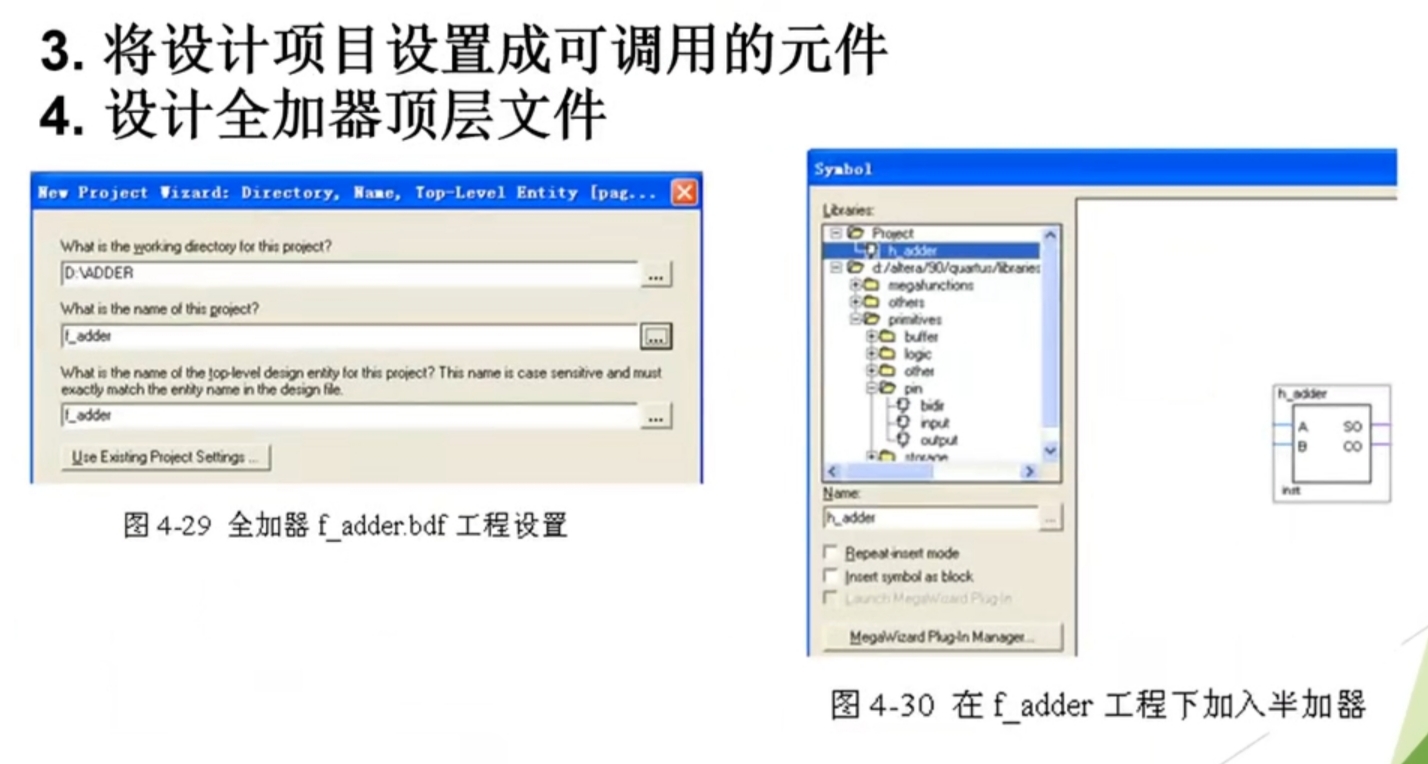

电路原理图设计流程

封装设计

在已经设计好锁存器的基础上:

File->Create/Update->Create Symbol Files for Current File

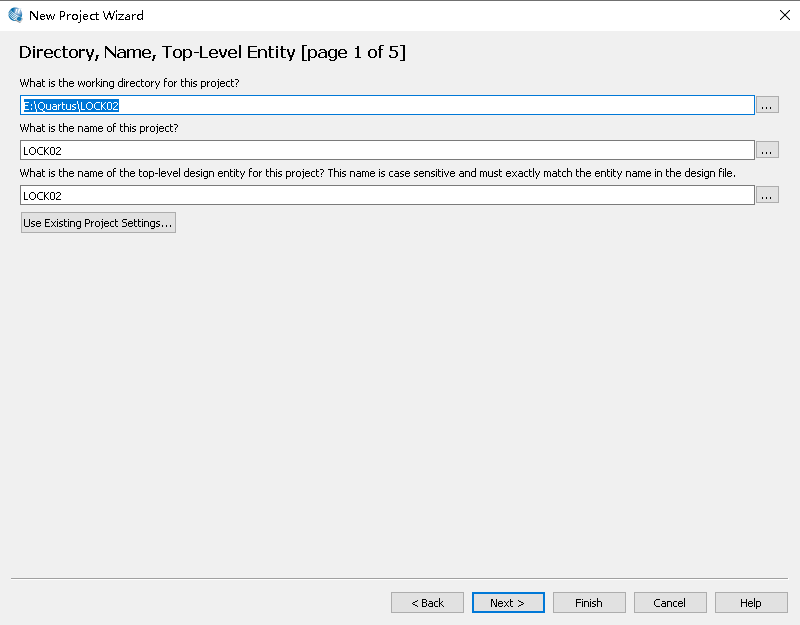

这时新建一个工程:File->New->Block Diagram/Schematic File;然后保存;保存过后点击File->New Project Wizard;

选择新建的项目:

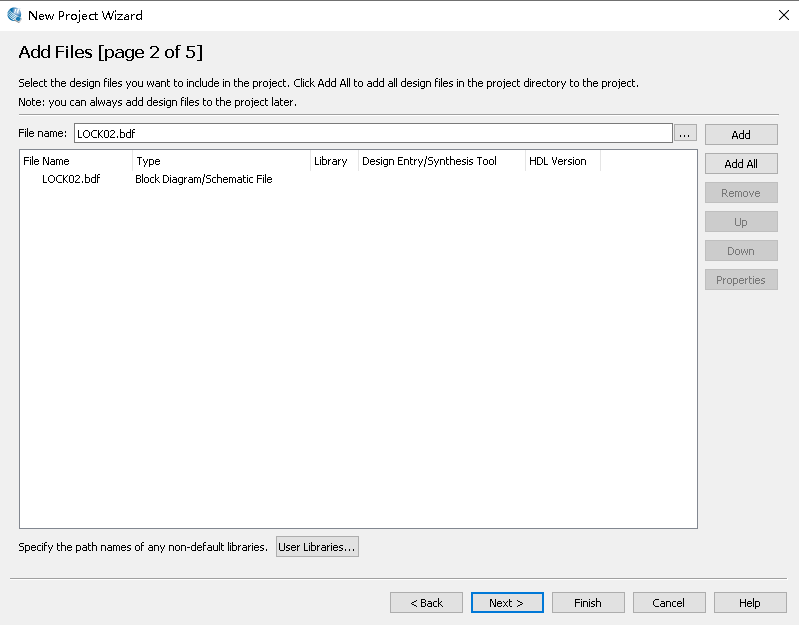

添加文件进去:

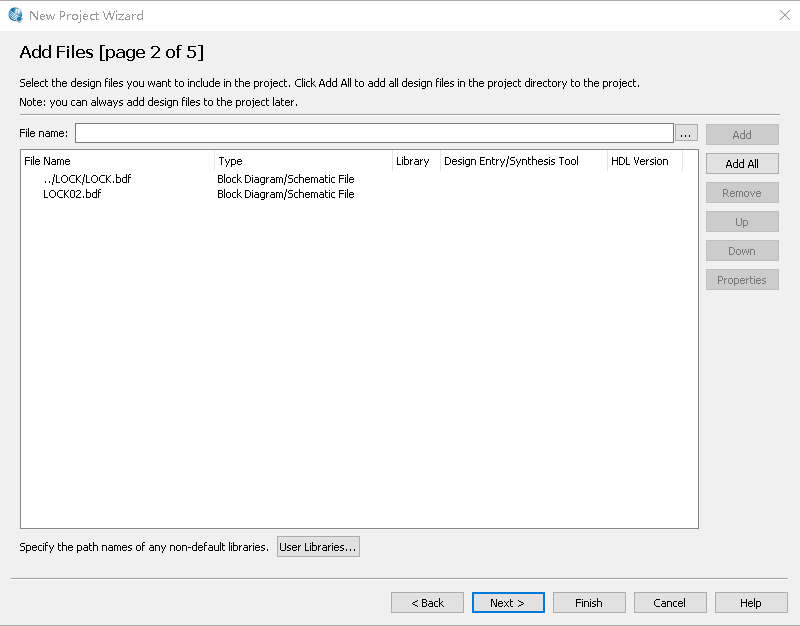

还要将之前的文件添加进去:

然后选择芯片:Cyclone 3->EP3C40Q240C8(实验室使用:EP3C16Q240C8);点击Next,一直到Finish.

右键:选择Insert->Symbol

然后点击左下角3个点(…);选择LOCK.bsf文件(原理图设计文件);即可以插入了,添加输入输出端,编译,然后进行仿真即可.

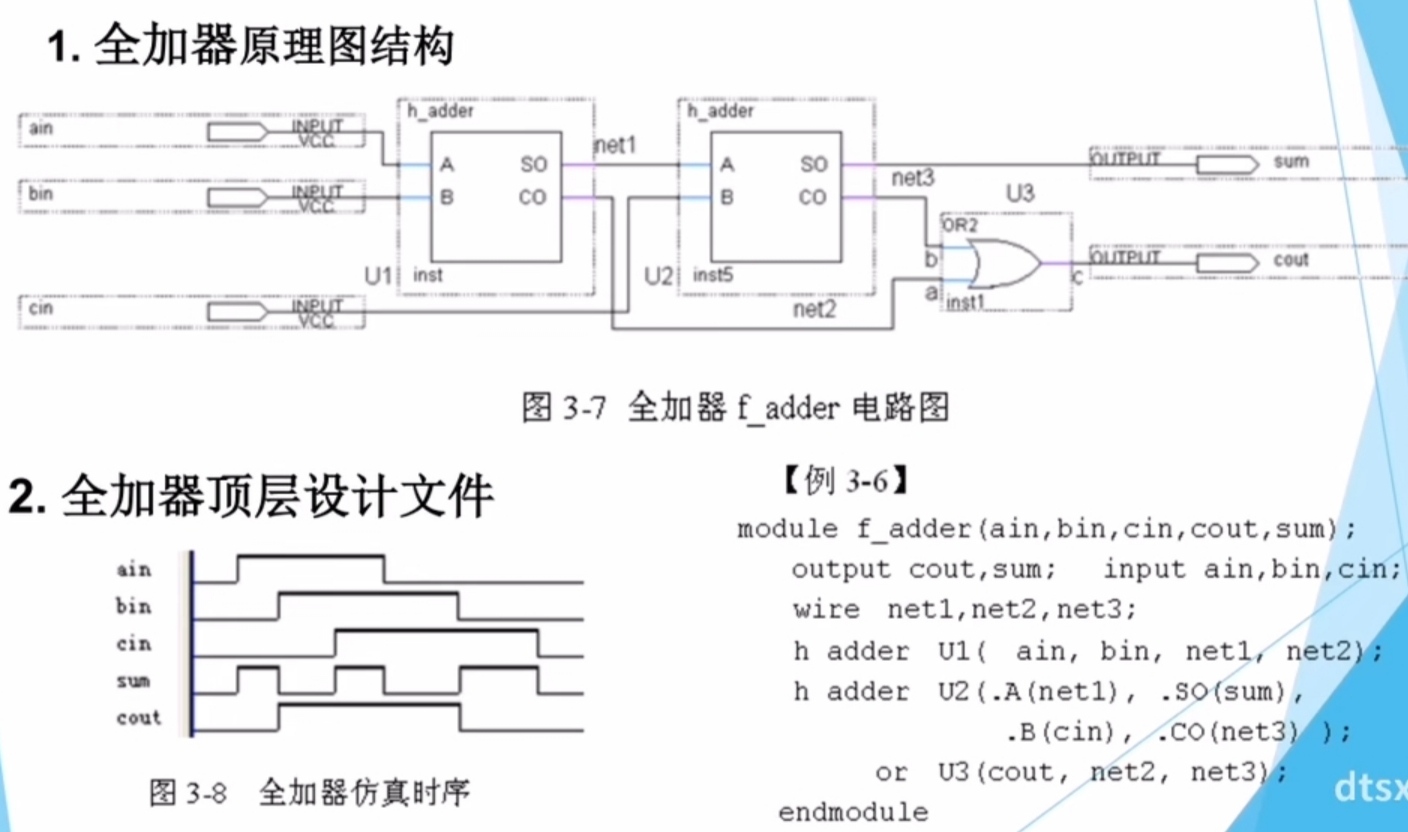

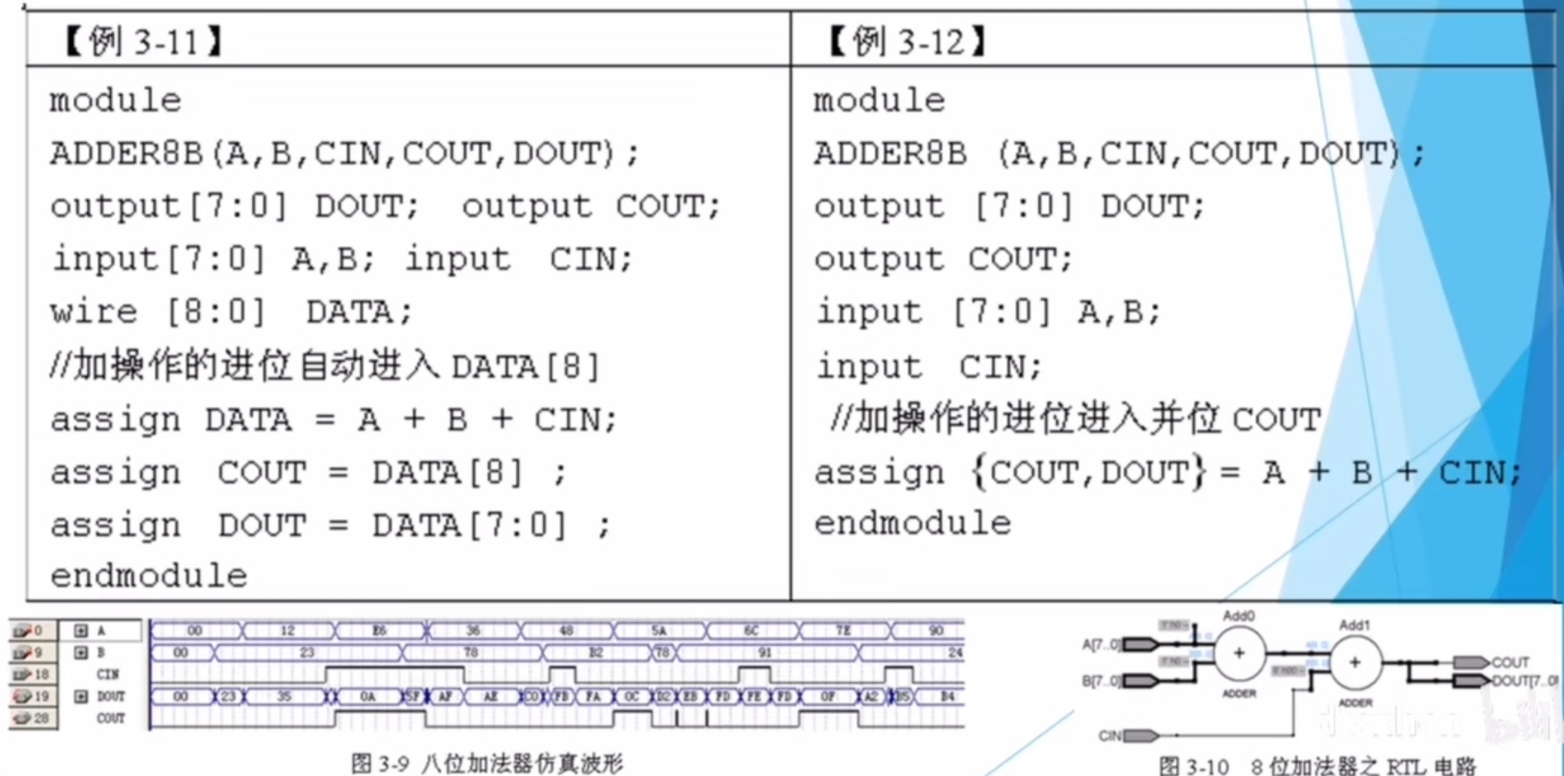

Verilog加法器设计

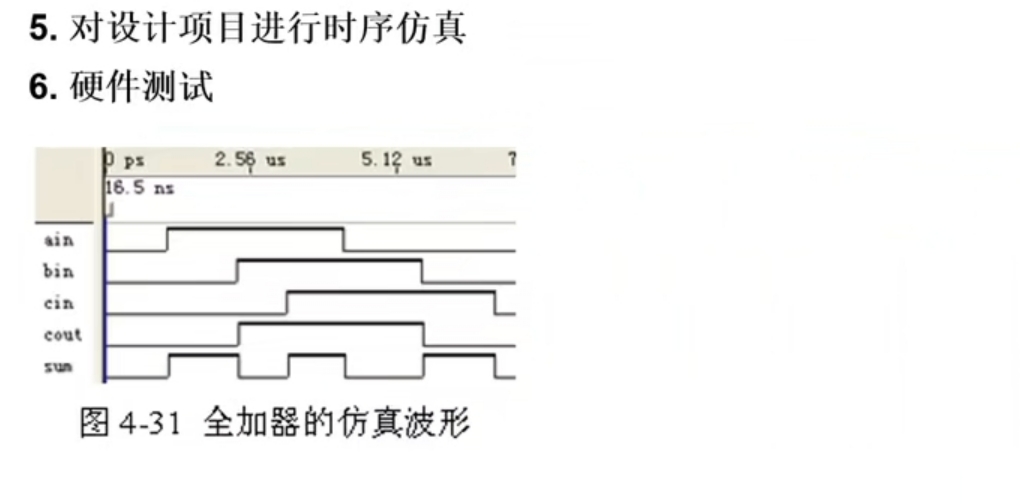

全加器设计

3.Verilog例化语句及其用法

1 | <模块元件名> <例化元件名> (.例化元件端口 (例化元件外接端口名),...); |

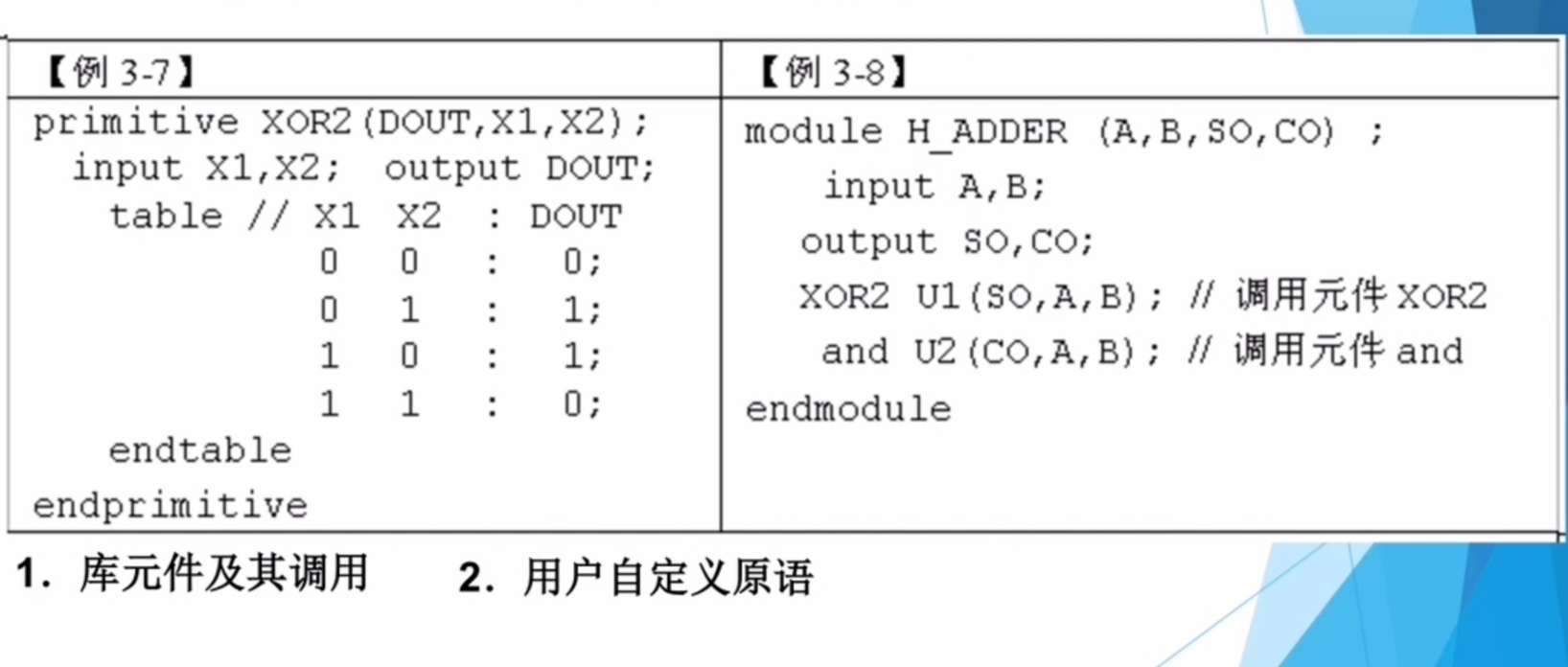

半加器的UDP结构建模描述方法

利用UDP元件设计多路选择器

1 | primitive MUX41_UDP(Y,D3,D2,D1,D0,S1,S0) ; |

1 | module MUX41UDP (D,S,DOUT); |